功耗调整指引

1. 打开/关闭 组件¶

1.1. 可选的组件¶

在Tiramisu系列芯片上可选使能的组件有 : ETH 、USB 和 SATA

1.2. ETH¶

需要在U-Boot及Linux Kernel进行调整才能完全关闭该组件

1.2.1 调整U-Boot¶

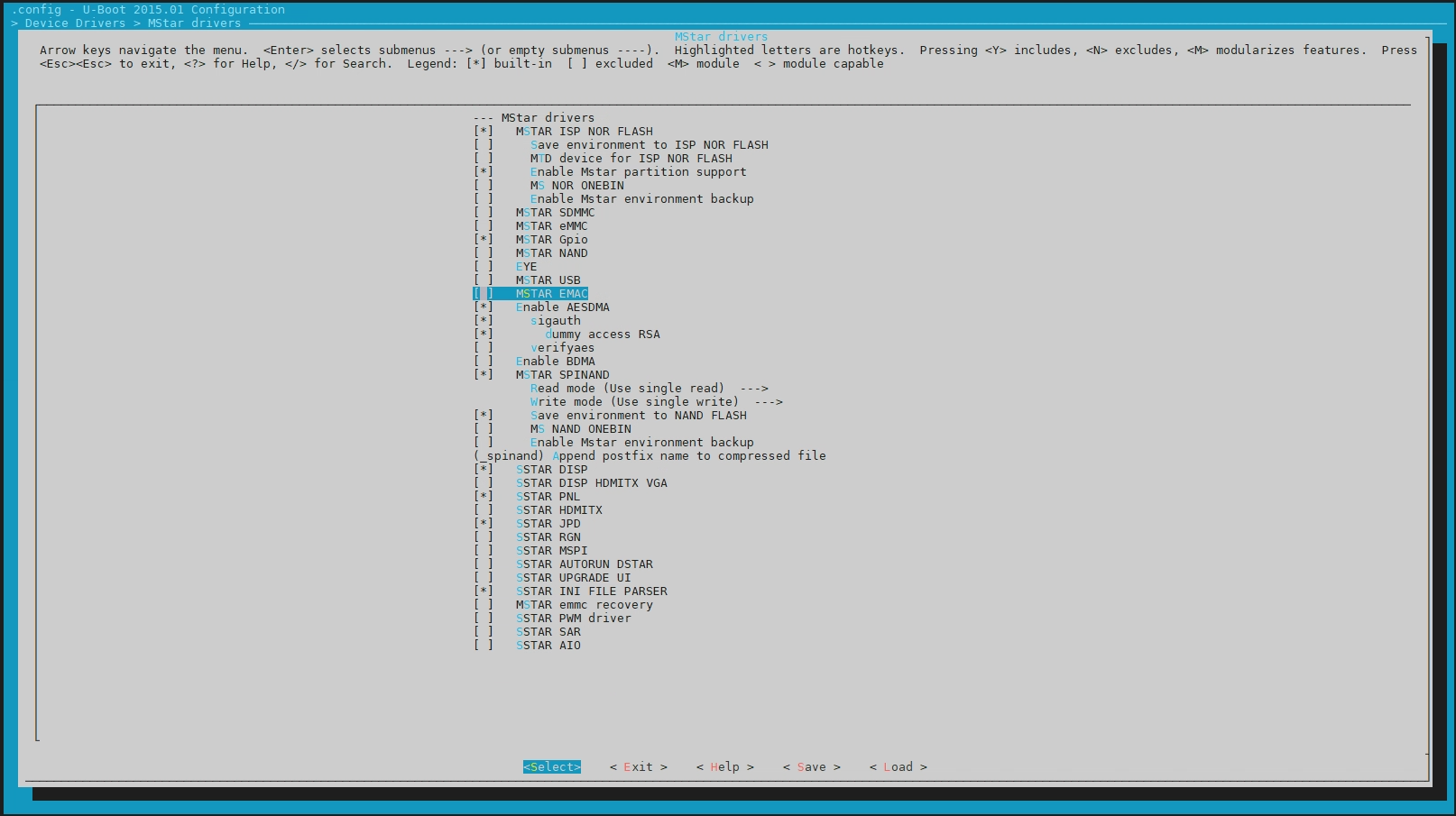

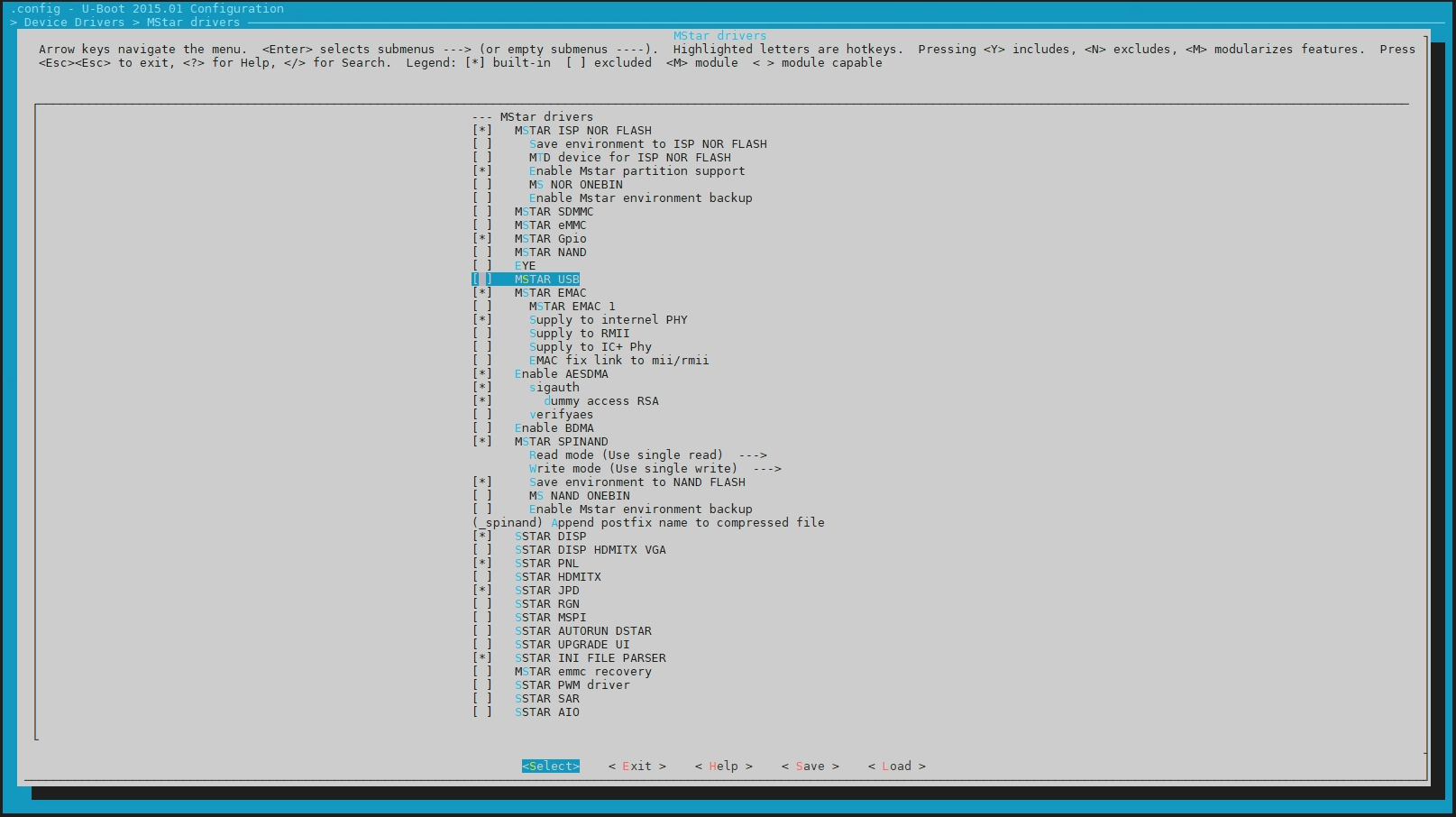

Step1. 取消MSTAR EMAC的选项

1.2.2 调整Linux Kernel¶

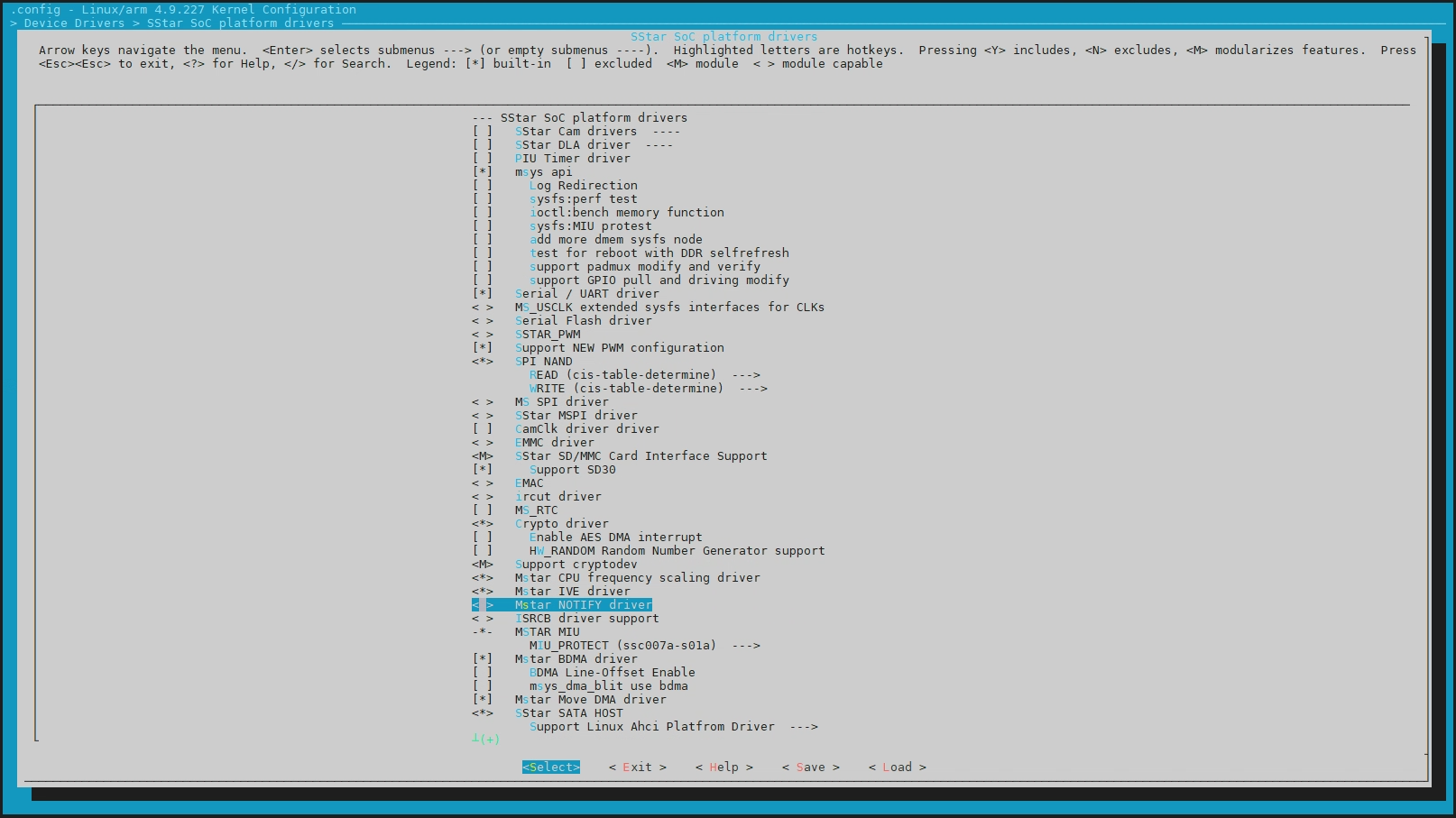

Step1.取消EMAC的选项

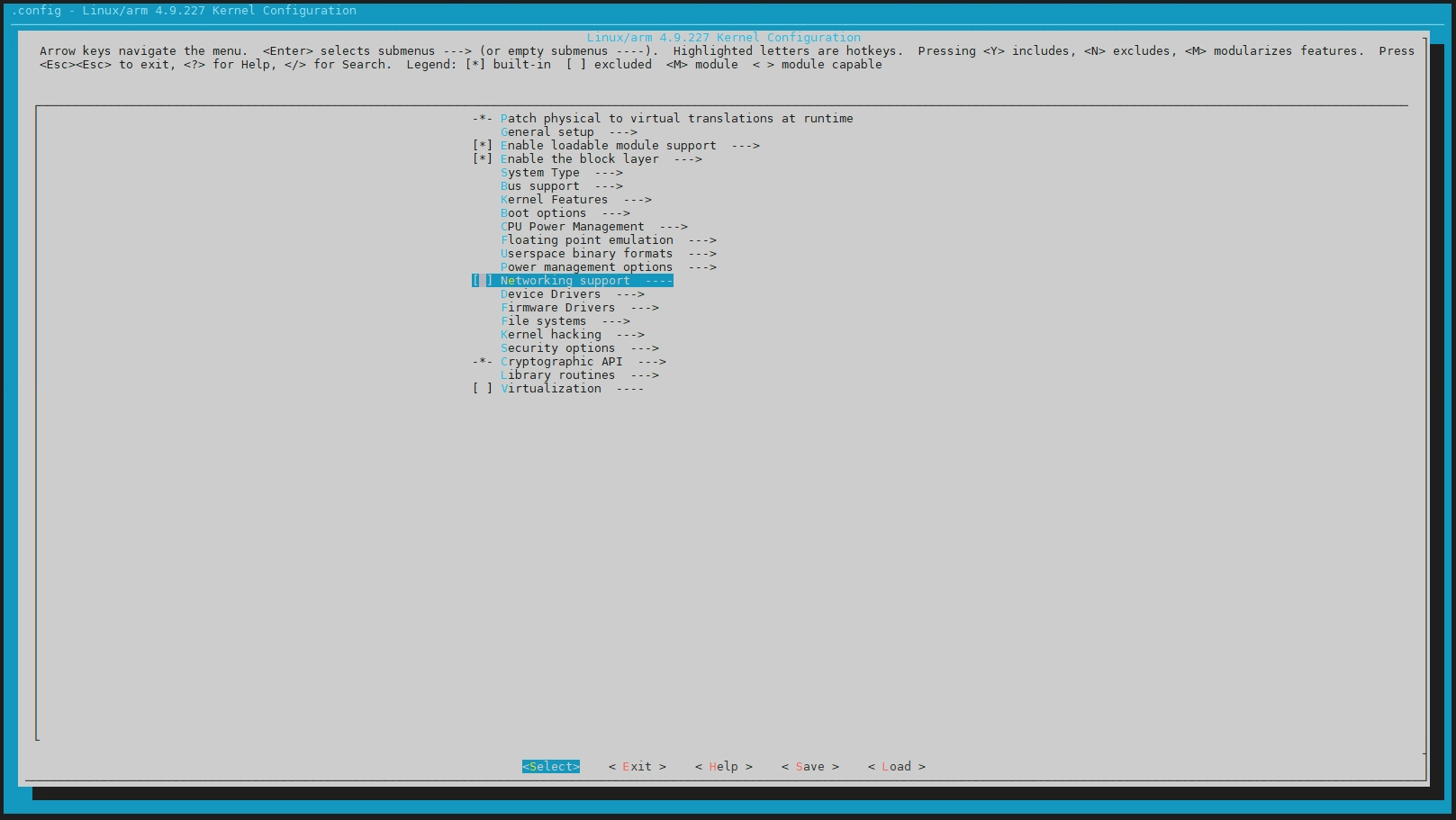

Step2. 取消Networking support的选项

Step3. 取消Mstar NOTIFY driver的选项

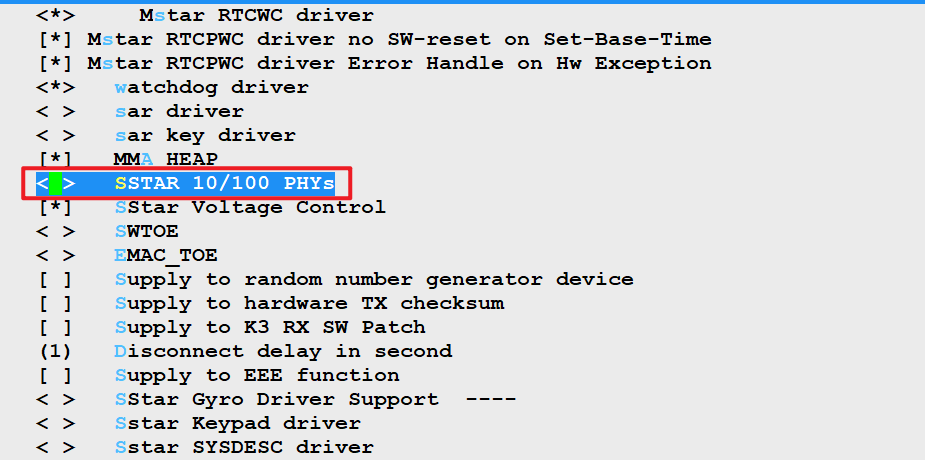

Step4. 取消SSTAR 10/100 PHYs的选项

1.3. USB¶

需要在U-Boot及Linux Kernel进行调整才能完全关闭该组件

1.3.1 调整U-Boot¶

Step1. 取消MSTAR USB的选项

1.3.2 调整Linux Kernel¶

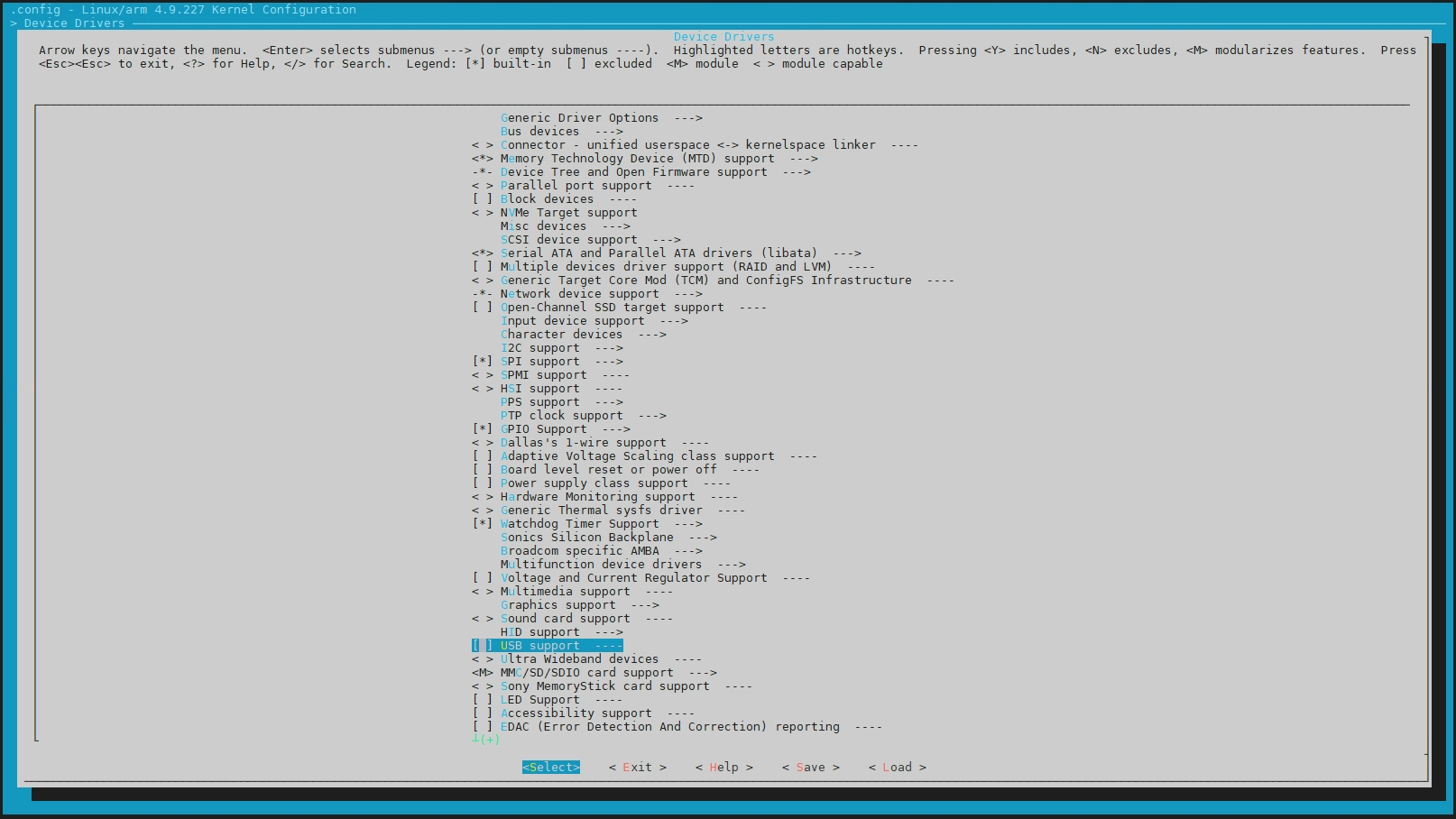

Step1. 取消USB选项

1.4. SATA¶

调整Kernel Config就可以关闭 SATA组件

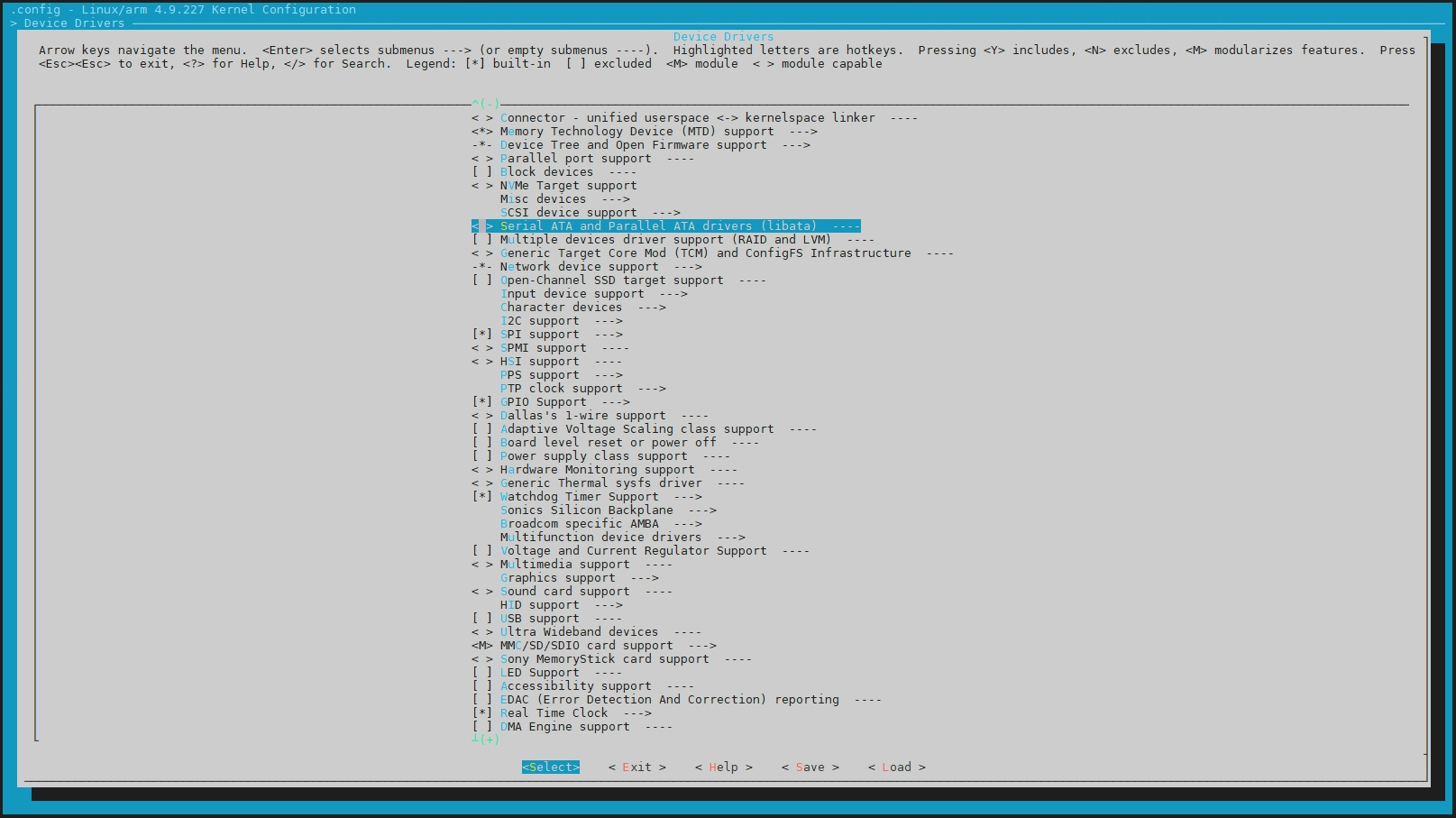

Step1. 取消Kernel SATA Support

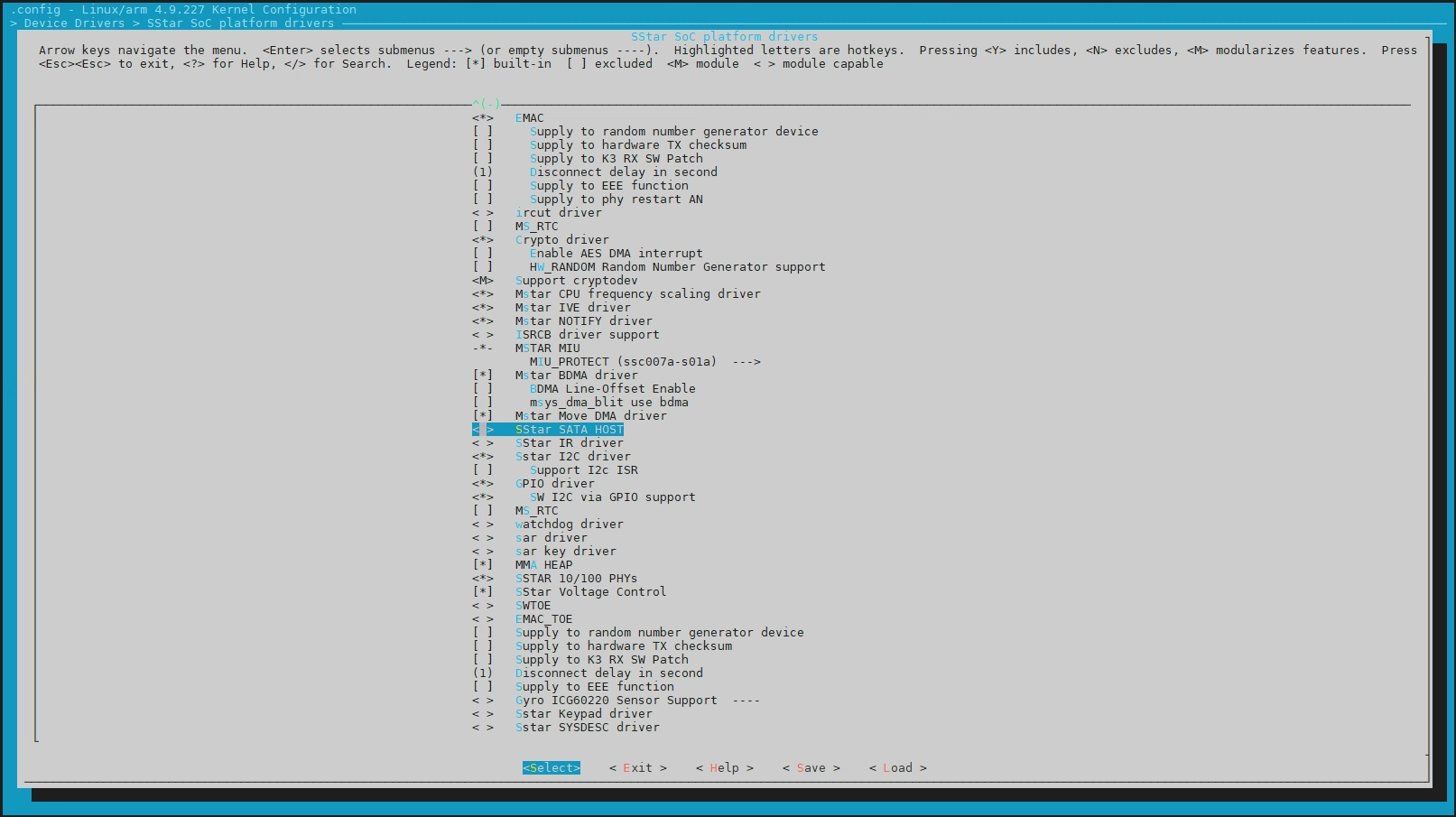

Step2. 取消SStar SATA Driver

2. 组件时钟频率配置¶

2.1. MIU clock & MIUPLL¶

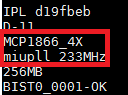

2.1.1 DDR时钟频率配置¶

可以通过选用不同的IPL及IPL_CUST文件(在project/board/m6/boot/ipl目录下)来设置DDR的频率。注意,内存频率可向下兼容,反之则不行。如2133频率的DDR可以使用2133、1866、1600的IPL,而1866频率的DDR则只能使用1866、1600的IPL,不能使用2133的IPL。

2.2. CPU 时钟频率配置¶

2.2.1 Voltage scaling 配置¶

Core Power :

cat /sys/devices/system/voltage/core_power/voltage_current

Cpu Power :

cat /sys/devices/system/voltage/cpu_power/voltage_current

Dla Power :

cat /sys/devices/system/voltage/dla_power/voltage_current

注:920G已调整core_power/cpu_power/dla_power控制逻辑,应用层无需控制,只有2档可调,系统会根据VOLTAGE_DEMANDER_TEMPERATURE动态调整,

默认为1000,当IC内部温度超过一定范围会自动降到900。

2.2.2 Clock scaling 配置¶

-

Read current CPU frequency

cat /sys/devices/system/cpu/cpufreq/cpufreq_testout -

Update CPU frequency

echo x > /sys/devices/system/cpu/cpufreq/policy0/scaling_min_freq echo x > /sys/devices/system/cpu/cpufreq/policy0/scaling_max_freq x = 800000, 1000000, 1100000, 1200000

Example:

echo 1000000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_min_freq echo 1000000 > /sys/devices/system/cpu/cpufreq/policy0/scaling_max_freq

默认min cpufreq = 800MHz

# cat /sys/devices/system/cpu/cpufreq/cpufreq_testout 800016000

如修改min cpufreq为1000MHz

# cat /sys/devices/system/cpu/cpufreq/policy0/scaling_min_freq 1000000 # cat /sys/devices/system/cpu/cpufreq/policy0/scaling_max_freq 1200000 # cat /sys/devices/system/cpu/cpufreq/cpufreq_testout 1000032000

2.3. ISP 时钟频率配置¶

2.3.1 ISP配置示例¶

在isp.ko, ispmid.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的isp clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/isp0/isp_clk -

设置isp clock rate,可通过以下命令设置

echo 240000000 > /sys/devices/virtual/mstar/isp0/isp_clk

2.3.2 ISP时钟频率档位¶

-

480000000

-

432000000

-

384000000

-

320000000

-

240000000

-

216000000

-

172800000

-

72000000

2.3.3 约束¶

以上的设置应该在模块加载完成之后操作模块功能之前设置,才能正确的生效。

2.4. 编解码时钟频率配置¶

2.4.1 编解码器配置示例¶

在mhal.ko加载之后,开启视频编解码处理任务之前,即可通过如下命令设置相关频率:

Vcodec Firmware跑在一颗独立的Cpu(Vcpu),且HW ip与ven arbiter clk分别单独控制,因此有三个Clk: Vcpu(SW), HW ip , ven arbiter(AXI), 分别透过ven_clock, ven_clock_2nd, ven_clock_axi控制

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/venc/ven_clock cat /sys/devices/virtual/mstar/venc/ven_clock_2nd cat /sys/devices/virtual/mstar/venc/ven_clock_axi

-

设置clock rate,可通过以下命令设置

echo 320000000 > /sys/devices/virtual/mstar/venc/ven_clock echo 320000000 > /sys/devices/virtual/mstar/venc/ven_clock_2nd echo 320000000 > /sys/devices/virtual/mstar/venc/ven_clock_axi

2.4.2 编解码器时钟频率档位¶

-

ven_clock

-

468000000

-

420000000

-

348000000

-

300000000

-

480000000

-

432000000

-

384000000

-

320000000

-

288000000

-

192000000

-

123400000

-

-

ven_clock_2nd

-

468000000

-

420000000

-

348000000

-

300000000

-

216000000

-

384000000

-

320000000

-

-

ven_clock_axi

-

468000000

-

420000000

-

348000000

-

300000000

-

384000000

-

320000000

-

216000000

-

2.4.3 约束¶

-

以上的设置应该在模块加载完成之后操作模块功能之前设置,并在执行模块时才能正确的生效。

-

当ven_clock, ven_clock_2nd, ven_clock_axi其中一个设定为 468000000/ 420000000/ 348000000/ 30000000时,另外两个只能选择相同的CLk或者除此之外的其它Clk,即ven_clock, ven_clock_2nd和ven_clock_axi不能同时为其中的不同值。

2.5. SCL 时钟频率配置¶

2.5.1 scaler时钟频率配置¶

在mhal.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/mscl/clk -

设置clock rate,可通过以下命令设置

echo 384000000 > /sys/devices/virtual/mstar/mscl/clk

2.5.2 scaler时钟频率档位¶

-

480000000 (OD)

-

432000000

-

384000000

-

320000000

-

288000000

-

240000000

-

172000000

-

123000000

2.5.3 约束¶

以上的设置应该在模块加载完成之后操作模块功能之前设置,并在执行模块时才能正确的生效。

2.6. LDC 时钟频率配置¶

2.6.1 LDC时钟频率配置¶

在mhal.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/ldc/clk -

设置clock rate,可通过以下命令设置

echo 384000000 > /sys/devices/virtual/mstar/ldc/clk

2.6.2 LDC时钟频率档位¶

-

480000000 (OD)

-

432000000

-

384000000

-

320000000

-

288000000

-

216000000

-

86000000

2.7. JPEG 时钟频率配置¶

2.7.1 JPEG时钟频率配置¶

在mhal.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/jpeg/jpe_clock -

设置clock rate,可通过以下命令设置

echo 432000000 > /sys/devices/virtual/mstar/jpeg/jpe_clock

2.7.2 JPEG时钟频率档位¶

-

480000000

-

432000000

-

384000000

-

320000000

-

288000000

-

216000000

2.8. IVE 时钟频率配置¶

2.8.1 IVE时钟频率配置¶

在mhal.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得(Bank 1038 h6a [12:8] reg_ckg_ive)

/customer/riu_r 1038 6a -

设置clock rate,可通过以下命令设置

/customer/riu_w 1038 6a XXYY XX : IVE clock YY : origin value (use riu_r to check this value)

2.8.2 IVE时钟频率档位¶

-

XX=00001 : disable clock

-

XX=00000 : 216 MHz

-

XX=00100 : 172 MHz

-

XX=01000 : 123 MHz

-

XX=01100 : 86 MHz

-

XX=10000 : 288 MHz

-

XX=10100 : 320 MHz

2.9. IPU 时钟频率配置¶

2.9.1 IPU时钟频率配置¶

mi_ipu.ko加载后,可以通过写时钟频率(单位MHz)到/sys/dla/clk_rate配置IPU时钟频率

Example:

echo 900 > /sys/dla/clk_rate

2.9.2 IPU时钟频率档位¶

# cat /sys/dla/clk_rate current ipu clock frequency: 900MHz available frequency: 300MHz 400MHz 500MHz 600MHz 700MHz 800MHz 900MHz 1000MHz

2.10. 观察cpu的温度¶

cat /sys/devices/virtual/mstar/msys/TEMP_R

结果仅供参考,因为误差可以达到5摄氏度。

2.11. MOP/DISP 时钟频率配置¶

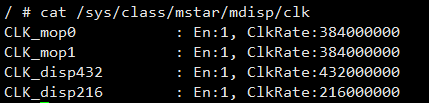

DISP / MOP 有4 CLK, mop0/mop1/disp432/disp216。其中disp432/disp216是固定檔位無法調整。

2.11.1 MOP时钟频率配置¶

在mhal.ko加载之后,开启视频处理任务之前,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/mdispl/clk

-

设置clock rate,可通过以下命令设置

打开mop0

echo mop0 1 384000000 > /sys/devices/virtual/mstar/mdisp/clk关闭mop0

echo mop0 0 384000000 > /sys/devices/virtual/mstar/mdisp/clk打开mop1

echo mop1 1 384000000 > /sys/devices/virtual/mstar/mdisp/clk关闭mop1

echo mop1 0 384000000 > /sys/devices/virtual/mstar/mdisp/clk

2.11.2 MOP时钟频率档位¶

-

480000000

-

432000000

-

384000000

-

320000000

-

288000000

-

240000000

-

216000000

-

192000000

2.11.3 约束¶

以上的设置应该在模块加载完成之后操作模块功能之前设置,并在执行模块时才能正确的生效。

2.12. PNL 时钟频率配置¶

PNL CLK因要配合output interface的規格。無法作調整。

2.13. GE 时钟频率配置¶

2.13.1 GE时钟频率配置¶

在mhal.ko加载之后,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/mge/geclk GE Now_clk equal miu clk ======================== GE Clk Msg ======================== 216000000 172800000 144000000 320000000 384000000 432000000 240000000

-

设置clock rate,可通过以下命令设置

echo 0 clk=384000000 > /sys/devices/virtual/mstar/mge/geclk

2.13.2 GE时钟频率档位¶

-

216000000

-

172800000

-

144000000

-

320000000

-

384000000

-

432000000

-

240000000

GE Clock (Bank 1038 h51 [4:0])

/customer/riu_r 1038 51

2.14. JPD 时钟频率配置¶

2.14.1 JPD时钟频率配置¶

在mhal.ko加载之后,开启图片解码任务之后,即可通过如下命令设置相关频率:

-

读取目前的clock rate,可通过以下命令取得

cat /sys/devices/virtual/mstar/jpd/jpdclk -

设置clock rate,可通过以下命令设置

echo 0 clk=432000000 > /sys/devices/virtual/mstar/jpd/jpdclk //0 -> dev0

2.14.2 JPD时钟频率档位¶

-

432000000

-

384000000

-

320000000

-

288000000

-

172800000

-

240000000

jpd Clock (Bank 1038 h4a [4:0])

2.15. HDMI 时钟频率配置¶

2.15.1 HDMI时钟频率配置¶

在mhal.ko加载之后,即可通过如下命令设置相关频率:

-

关闭时钟:

echo disp432 0 4320000000 > /sys/devices/virtual/mstar/mhdmitx/clk -

开启时钟:

echo disp432 1 4320000000 > /sys/devices/virtual/mstar/mhdmitx/clk

2.15.2 HDMI时钟频率档位¶

(目前只支持432M clk)

echo disp432 1 4320000000 > /sys/devices/virtual/mstar/mhdmitx/clk echo disp216 1 2160000000 > /sys/devices/virtual/mstar/mhdmitx/clk

disp432 Clock (Bank 1038 h48 [11:8])

3. Check list¶

3.1. CPU Voltage¶

Core Power :

cat /sys/devices/system/voltage/core_power/voltage_current

Cpu Power :

cat /sys/devices/system/voltage/cpu_power/voltage_current

Dla Power :

cat /sys/devices/system/voltage/dla_power/voltage_current

3.2. CPU Clock¶

cat /sys/devices/system/cpu/cpufreq/cpufreq_testout

3.3. MIU Clock & MIUPLL¶

3.4. ISP Clock (Bank 1038 h61 [12:8])¶

/customer/riu_r 1038 61

3.5. VEN Clock (Bank 1038 h68 [4:0] & h69 [3:0] & h69 [11:8])¶

/customer/riu_r 1038 68

/customer/riu_r 1038 69

3.6. VPE Clock (Bank 1038 h64 [4:0])¶

/customer/riu_r 1038 64

3.7. LDC Clock (Bank 1038 h53 [4:0])¶

/customer/riu_r 1038 53

3.8. DIP Clock (Bank 1038 h52 [4:0])¶

/customer/riu_r 1038 52

3.9. JPEG Clock (Bank 1038 h6a [4:0])¶

/customer/riu_r 1038 6a

3.10. IVE Clock (Bank 1038 h6a [12:8])¶

/customer/riu_r 1038 6a

3.11. IPU Clock (Bank 1038 h50 [4:0])¶

/customer/riu_r 1038 50

3.12. EMAC Clock (Bank 1038 h42 [3:0])¶

/customer/riu_r 1038 42

3.13. Mop0 Clock (Bank 1038 h47 [4:0])¶

/customer/riu_r 1038 47

3.14. Mop1 Clock (Bank 1038 h47 [12:8])¶

/customer/riu_r 1038 47

3.15. JPD Clock (Bank 1038 h4a [12:8])¶

/customer/riu_r 1038 4a

3.16. GE Clock (Bank 1038 h51 [12:8])¶

/customer/riu_r 1038 51

3.17. HDMI Clock (Bank 1038 h48 [11:8])¶

/customer/riu_r 1038 48